Semiconductor IP

Color Space Converter & Chroma Resampler

#### **General Description**

The Digital Blocks DB1825 Color Space Converter & Chroma Resampler Verilog IP Core transforms 4:4:4 sampled RGB color components to 4:4:4 Y'CbCr color space followed by Chroma Resampling to 4:2:2 sampled Y'CbCr color components.

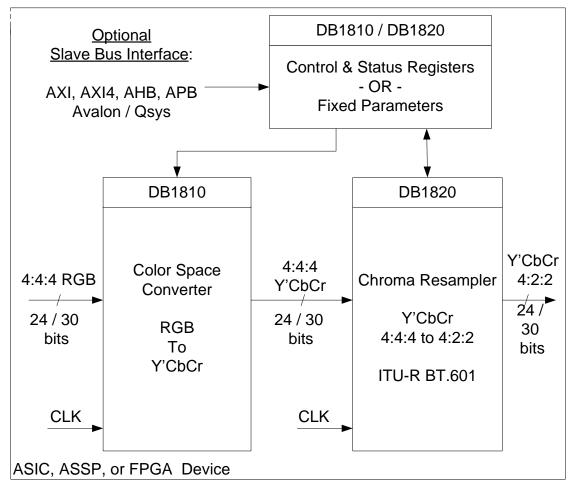

Figure 1 depicts the DB1825 Color Space Converter (CSC) & Chroma Resampler (CR) IP Core embedded within an integrated circuit device. Control & Status, including the CSC transforms coefficients and the CR decimating filters coefficients, can be programmed into optional DB1825 registers via a bus interface, or set as non-register fixed parameters at synthesis for a smaller VLSI footprint.

Figure 1: DB1825 Color Space Converter & Chroma Resampler

The DB1825 builds on the Digital Blocks DB1810 Color Space Converter IP Core and the DB1820 Chroma Resampler IP Core.

## **DB1810 - Color Space Converter**

# **Color Space Matrix Transform**

The DB1810 Color Space Converter performs the following 4x4 matrix transform (with summands  $S_1S_2S_3$ ), where  $X_1X_2X_3$  represents the input 4:4:4 sampled RGB color components and  $Y_1Y_2Y_3$  the 4:4:4 sampled Y'CbCr color component outputs:

$$\begin{bmatrix} C_{11} \ C_{12} \ C_{13} \ S_1 \\ C_{21} \ C_{22} \ C_{23} \ S_2 \\ C_{31} \ C_{32} \ C_{33} \ S_3 \end{bmatrix} \begin{bmatrix} X_1 \\ X_2 \\ X_3 \\ 1 \end{bmatrix} = \begin{bmatrix} Y_1 \\ Y_2 \\ Y_3 \end{bmatrix}$$

Digital Blocks Applications Engineering provides the coefficients for the Color Space Converter.

#### **DB1810 Color Space Converter - Features**

- $X_1X_2X_3$  and  $Y_1Y_2Y_3$  input & output components (for example,  $X_1X_2X_3 = RGB$  input;  $Y_1Y_2Y_3 = Y$ 'CrCb output) each at 8- or 10-bits, unsigned data type. User selectable at 24- or 30-bit parallel or serial input / output.

- Coefficients are 10-bit signed fractional data type & Summands are 17-bit Signed, integer data type

- After conversion, each Y<sub>1</sub>Y<sub>2</sub>Y<sub>3</sub> sample component can be truncated or roundedup, and saturated or clamped for overflow or underflow, respectively

# **DB1820 – Chroma Resampler**

The Digital Blocks DB1820 Chroma Resampler IP Core down converts 4:4:4 Y'CbCr to 4:2:2 Y'CbCr in accordance with the ITU-R BT.601 standard requirements.

The DB1820 Chroma Resampler decimates by 2 the CbCr color components in addition to providing anti-aliasing filtering.

## **DB1820 Chroma Resampler - Features**

- 4:4:4 Y'CbCr and 4:2:2 Y'CbCr input & output components each at 8- or 10-bits, unsigned data type. User selectable at 24- or 30-bit parallel or serial input / output.

- Coefficients are 3-bit fractional data type

- Control signal enable for start-up and blanking period disabling

- After down conversion, each CbCr sample component can be truncated or rounded-up, and saturated or clamped for overflow or underflow, respectively

- Equalization of Y' component and optional delay for display VSYNC, HSYNC, and DE signals

#### DB1825 Color Space Converter & Chroma Resampler - Features

- User optional Slave Bus Interface for programming Control & Status Registers, which includes the converters coefficients or fixed parameters set at synthesis

- Member of Digital Blocks' *Video Signal & Image Processing IP Core Family*, which include the following:

- o DB1800 Standard Definition NTSC/PAL/SECAM Video Sync Separator

- o DB1810 Color Space Convert

- o DB1820 Chroma Resampler

- DB1825 RGB to YCrCb Color Space Convert with 4:4:4 to 4:2:2 Chroma Resampler

- o DB1830 BT.656 Encoder

- o DB1840 BT.656 Decoder

- o DB1892 RGB to CCIR601/656 Encoder

- On-Chip Interconnect Compliance (optional) Avalon/Qsys, AXI, AXI4, AHB:

- o Avalon Interface Specification (MNL-AVABUSREF-2.0)

- o AMBA AXI Protocol Specification (V1.0)

- o AMBA AXI4 Protocol Specification (V3.0)

- o AMBA AHB Specification 2.0

- o AMBA APB Specification 2.0

- FPGA Integration Support:

- Altera Quartus II & Qsys / SOPC Integration & NIOS II EDS Reference Design

- Xilinx ISE Design Suite utilizing AMBA AXI4 & Embedded Development & Software Development Kits

- ASIC / ASSP Design-In Support:

- o Compliance to RTL Design & Coding Standards

- Digital Blocks Support Services

- Fully-synchronous, pipelined architecture, synthesizable Verilog RTL core

#### **Pin Description**

DB1825 Color Space Converter & Chroma Resampler IP Core contains optional AMBA bus AXI, AXI4, AHB, APB and Avalon / Qsys bus for processor programming of internal parameters. The DB1825 optionally contains no bus interface with hard-coding of the video transformation parameters.

The DB1825 contains the following I/O interface. For information on a bus fabric interface I/O, please contact Digital Blocks.

| Name             | Type   | Description                          |

|------------------|--------|--------------------------------------|

| Input Interface  |        |                                      |

| CSC_PCLK         | Input  | CSC Sample Clock                     |

| CSC_PRESETN      | Input  | CSC Reset                            |

| CSC_R            | Input  | CSC R – Red Input Color Components   |

| CSC_G            | Input  | CSC G – Green Input Color Components |

| CSC_B            | Input  | CSC B – Blue Input Color Components  |

| CSC_IVLD         | Input  | CSC Input Valid (Optional)           |

| Output Interface |        |                                      |

| CR_Y_OUT         | Output | CR Y' – Luma Component               |

| CR_CB_OUT        | Output | CR Cb – Blue Chroma Component        |

| CR_CR_OUT        | Output | CR Cr – Red Chroma Component         |

| CR_CBCR_OUT      | Output | CR CBCR Muxed Blue Red Chroma        |

|                  |        | Components                           |

| CR_OVLD          | Output | CR Output Valid (Optional)           |

Table 1: DB1825 - I/O Pin Description of Color Space Converter & Chroma Resampler

Verification Method

The DB1825 contains a test suite with bus functional models that program the DB1825 control & status registers, drives the DB1825 with various standard component color

data, and checks expected results.

**Customer Evaluation**

Digital Blocks offers a variety of methods for prospective customers to evaluate the DB1825. These include Verilog simulations, encrypted FPGA models, or the DB1825

Demo System, which includes an Altera FPGA and 320x240 TFT LCD panel.

**Deliverables**

The DB1825 is available in FPGA netlist or synthesizable RTL Verilog, along with Synopsys Design Constrains, a simulation test bench with expected results, reference

design, and user manual.

Support

The DB1825 IP Core is warranted against defects. One year of phone and email technical support is included, starting with the first interaction. Additional maintenance and

support options are available.

**Ordering Information**

Please contact Digital Blocks for additional technical, pricing, evaluation, and support

information.

Digital Blocks, Inc.

PO Box 192

587 Rock Rd

Glen Rock, NJ 07452 USA

Phone: +1-201-251-1281

eFax: +1-702-552-1905

info@digitalblocks.com

Copyright © Digital Blocks, Inc. 2010-2017, ALL RIGHTS RESERVED

Digital Blocks TM is a registered trademark of Digital Blocks, Inc.

All other trademarks are the property of their respective owners