# Digital Blocks

## DB9100AVLN BitBLT Graphics HW Accelerator

Semiconductor IP

#### **General Description**

The Digital Blocks DB9100AVLN BitBLT Graphics Hardware Accelerator Verilog IP Core renders a graphics frame by generating new bitmaps from commands to combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Raster Operation (ROP) is a bitwise Boolean operation (such as AND, OR, XOR, NOT).

The DB9100AVLN also contains a Monochrome Bitmap Color Expansion feature, typically used for font expansion of compressed character bitmaps. A 1-bit depth bitmap is expanded to one of two colors, a foreground or background color, with the foreground color representing the text, and the background color the non-text background.

The DB9100AVLN also contains a programmable Alpha Blend unit, blending two bitmaps into one.

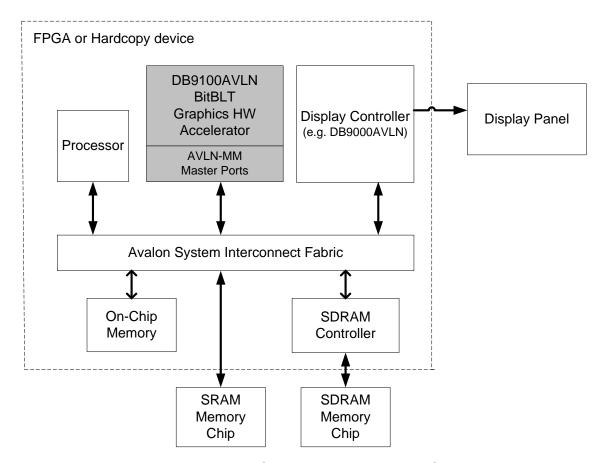

The DB9100AVLN interfaces to a microprocessor and frame buffer memory via the Altera Avalon Interconnect, providing a lower power solution. The DB9100AVLN contains a DMA Command Linked-List Processing Unit, for independently reading and processing graphics commands from the host processor.

Figure 1 depicts the system view of the DB9100AVLN BitBLT Graphics Hardware Accelerator Verilog IP Core embedded within an Altera FPGA or Hardcopy component.

Figure 1: DB9100AVLN BitBLT Graphics HW Accelerator - System Diagram

#### BitBLT Graphics Hardware Accelerator Verilog IP Features

- Bit Block Transfer 3 Independent Memory Sources of data:

- o On-Screen & Off-Screen Data Block (SRC)

- o Off-Screen Fixed Pattern Data Block (PTN)

- o On-Screen visible Data Block (DST)

- Raster Operations (ROP) performed on Block Transfers:

- o 256 Raster Operations

- o ROP0, ROP1, ROP2, & ROP3 operations

- o Includes industries most popular 16 ROPs

- BitBLT Draw Features:

- o Pixels, Horizontal & Vertical Lines

- o Overlapping & Non-Overlapping Block Transfers

- o Solid Color Block Fills

- FONT Monochrome Bitmap to Color Expansion, either Transparent or Opaque

- o Rotation Block Transfers: 0, 90, 180, 270 degrees

- o Block Stretch on X & Y Axis

- Alpha Blending

- o Sprite Moves

- Command FIFO or Link-List Display Processing Unit:

- o Simplifies Processor Interface

- o Minimizes Processor Overhead

- Frame Buffer & Display Features Supported:

- o Display Resolutions 4K x 4K

- o 4 GB Memory Range

- o 8, 16, 24, & 32 bits-per-pixel color depths

- Interrupt Controller with 3 sources of internal interrupts with masking control

- Reference Software Driver Included

- o Reference Driver

- o Graphics API Reference Design

- On-Chip Interconnect Compliance Avalon:

- o Avalon Interface Specification (MNL-AVABUSREF-2.0)

- FPGA Integration Support:

- Altera Quartus II & Qsys Integration & ARM / NIOS II EDS Reference Design

- o Xilinx Vivado IP Integrator & Reference Design

- ASIC / ASSP Design-In Support:

- o Compliance to RTL Design, Coding, & Verification Standards

- o Digital Blocks Support Services

- Compatible with Digital Blocks DB9000 Family of TFT LCD Controller IP Cores and Reference Designs

- Fully-synchronous, synthesizable Verilog RTL core.

#### **Deliverables**

The DB9100AVLN is available in RTL Verilog, along with synthesis scripts, a simulation test bench with expected results, reference design, datasheet, and user manual.

#### **Support**

The DB9100AVLN IP Core is warranted against defects for three years. One year of phone and email technical support is included, starting with the first interaction. Additional maintenance and support options are available.

### **Ordering Information**

Please contact Digital Blocks for additional technical, pricing, evaluation, and support information.

Digital Blocks, Inc. PO Box 192 / 587 Rock Rd Glen Rock, NJ 07452 USA Phone: +1-201-251-1281

Fax: +1-702-552-1905 info@digitalblocks.com

Copyright © Digital Blocks, Inc. 2007-2017, ALL RIGHTS RESERVED

Digital Blocks<sup>TM</sup> is a registered trademark of Digital Blocks, Inc. All other trademarks are the property of their respective owners.