Semiconductor IP

### **General Description**

The DB-I2C-S-APB-BRIDGE is an I<sup>2</sup>C Slave Controller IP Core focused on low VLSI footprint ASIC / ASSP designs not requiring internal configuration & control registers (and thus no local host CPU required). The DB-I2C-S-APB-BRIDGE processes the I<sup>2</sup>C protocol & physical layers, and receives & transmits bytes with respect to the I<sup>2</sup>C payload via a bridge APB Master Interface to user registers or memory.

The DB-I2C-S-APB-BRIDGE runs off the APB Master external clock input within the ASIC / ASSP, providing a synchronous design while offering I<sup>2</sup>C spike filtering of SDA and SCL.

The DB-I2C-S-APB-BRIDGE is a member of Digital Blocks DB-I2C Controller IP Core family, which includes I<sup>2</sup>C Master/Slave, I<sup>2</sup>C Master-only, and I<sup>2</sup>C Slave-only configurations.

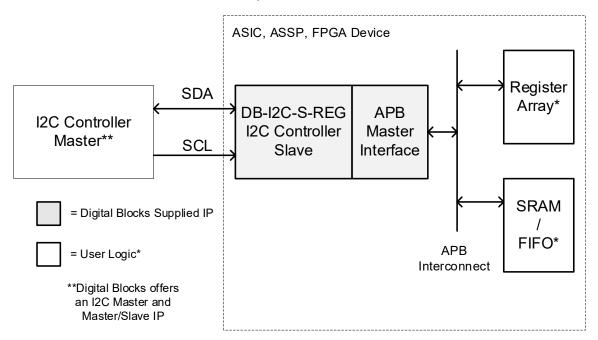

Figure 1 depicts the DB-I2C-S-APB-BRIDGE Core system view. The IP is configured by internal pre-synthesis parameters and post-synthesis top-level input signals, receives input clock and reset, and performs I<sup>2</sup>C Slave-Receiver transfers (for writing data to the APB via its APB Master Interface) and Slave-Transmitter transfers (for reading data from the APB via the APB Master Interface).

Figure 1: DB-I2C-S-APB-BRIDGE Controller - System View

#### Features

- I2C Slave Controller Implements Slave-only protocol for smaller VLSI footprint, for applications requiring Slave–Receiver and Slave–Transmitter capability

- APB Master Interface bridging the I<sup>2</sup>C Bus to the APB Bus

- Autonomous I2C Slave Controller:

- o No local CPU host required

- o No configuring of control/status registers

- Slave I<sup>2</sup>C Controller Modes:

- o Slave Transmitter

- o Slave Receiver

- Supports five I2C bus speeds:

- o Standard Mode (100 Kb/s)

- o Fast Mode (400 Kb/s)

- o Fast Mode plus (1 Mbit/s)

- Ultra fast mode (5 Mbit/s)

- o Hs-mode (3.4 Mbit/s)

- 7- or 10-bit I2C Slave ID addressing, SCL Low Wait States

- Digital filter for the received SDA and SCL lines

- Compliance with I2C specifications:

- o Philips The I2C-Bus Specification, Version 2.1, January 2000

- NXP Rev 7.0 October 1, 2021

- Fully-synchronous, synthesizable Verilog RTL core, with rising-edge clocking, no gated clocks, and no internal tri-states, for easy integration into FPGA or ASIC design flows.

# **Pin Description**

The DB-I2C-S-APB-BRIDGE I2C Slave Controller interface signals are listed in Table 1.

| Name                 | Type   | Description       |

|----------------------|--------|-------------------|

| I2C Bus Interface    |        |                   |

| SDAI                 | Input  | Serial Data       |

| SDAO                 | Output | Serial Data       |

| SCLI                 | Input  | Serial Clock Line |

| APB Master Interface |        |                   |

|                      |        |                   |

See AMBA 3 APB Protocol v2.0 Specification

Table 1: DB-I2C-S-APB-BRIDGE - I/O Pin Description

### Verification Method

The DB-I2C-S-APB-BRIDGE Controller IP Core contains a test suite that generates & sends I2C transactions, monitors the I2C bus protocol, and checks expected results.

### **Customer Evaluation**

Digital Blocks offers a variety of methods for prospective customers to evaluate the DB-I2C-S-APB-BRIDGE. Please contact Digital Blocks for additional information.

### **Deliverables**

The DB-I2C-S-APB-BRIDGE is available in synthesizable RTL Verilog or a technology-specific netlist for FPGAs, along with Synopsys Design Constraints, a simulation test bench with expected results, datasheet, and user manual.

# **Ordering Information**

Please contact Digital Blocks for additional technical, pricing, evaluation, and support information.

Digital Blocks, Inc. PO Box 192 587 Rock Rd Glen Rock, NJ 07452 USA Phone: +1-201-251-1281

eFax: +1-702-552-1905 info@digitalblocks.com

Copyright © Digital Blocks, Inc. 2007 - 2022, ALL RIGHTS RESERVED

###

Digital Blocks is a registered trademark of Digital Blocks, Inc. All other trademarks are the property of their respective owners