AXI4 Scatter-Gather DMA Controller – AXI4-Stream to/from AXI4 Memory Map Data Transfers

Digital Blocks offers Multi-Channel Scatter-Gather (SG) Direct Memory Access (DMA) Controllers that transfers data move between AXI4 Memory Map and AXI4-Stream Interfaces. The standard configuration is a two DMA Channel design targeting user requirement of two AXI4-Stream Interfaces, one each Master and Slave, transferring data to/from AXI4 Memory Mapped host memory. Up to 16 DMA Channel data mover designs available. Two versions are offered — SG Lists can be Descriptors setup in memory and read by the DMA Controller, or Commands written into the DMA Controller via dedicated AXI4-Stream interface.

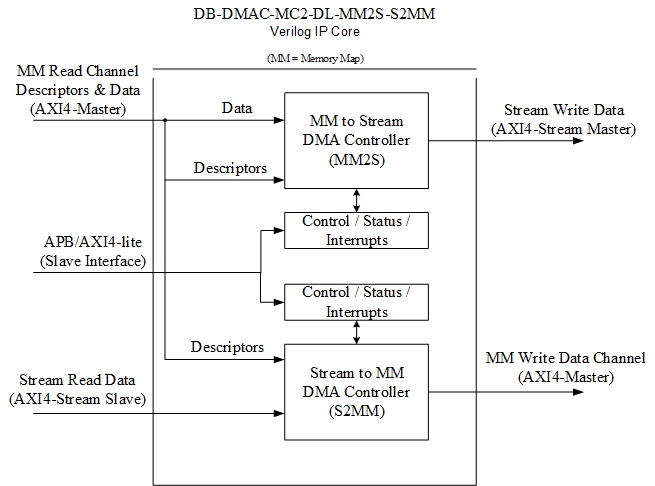

SG Lists Descriptors Read by DMA Controller

The DB-DMAC-MC2-DL-MM2S-S2MM (verilog IP core DB-DMAC-MC2-DL-MM2S-S2MM) transfers data under control of Scatter-Gather Descriptor lists. The Descriptors are read from memory via the AXI4 MM Read Channel.

For the DB-DMAC-MC2-DL-MM2S-S2MM version that reads in Scatter-Gather Descriptor lists, there are further versions: First is a high-performance version, that DMA data reads across Descriptors can keep going, thus providing high AXI data bandwidth capability; Second is lower performance, that processes one descriptor to completion at a time. This version requires less VLSI resources and licenses at a lower cost.

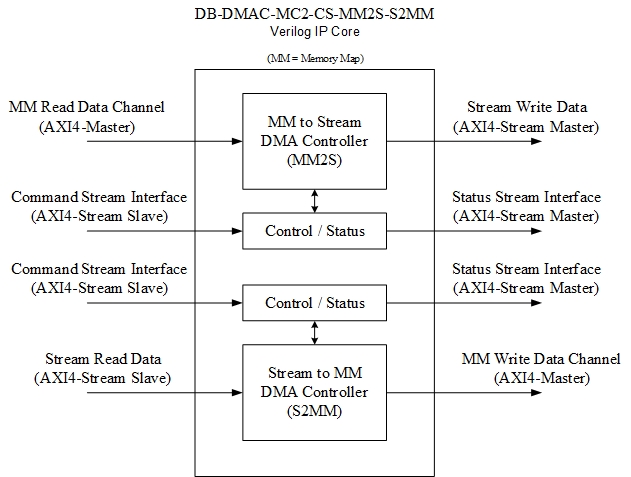

SG Lists Commands Written to the DMA Controller

The DB-DMAC-MC2-CS-MM2S-S2MM (verilog IP core DB-DMAC-MC2-CS-MM2S-S2MM) transfers data under control by Commands that stream in via dedicated Command, AXI4-Stream Interfaces, with resulting output Status on Status Stream, AXI4-Stream Interfaces.

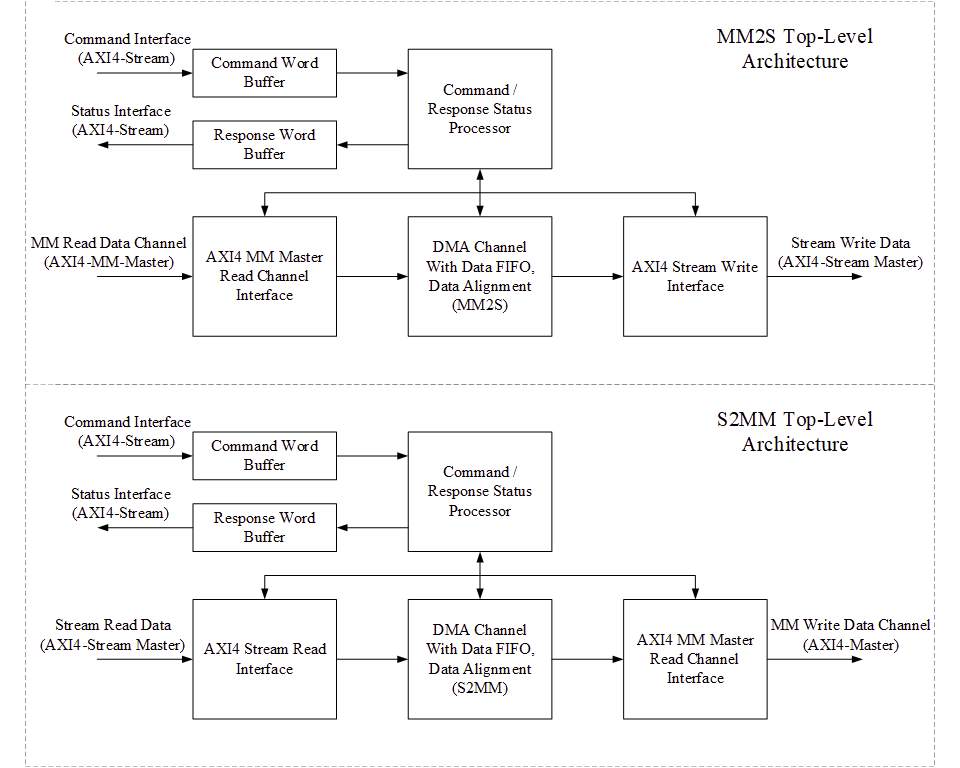

A high-level RTL Microarchitecture view of the low performance version (with lower VLSI resources, lower licensing cost) DMA datamover, between AXI4 Memory Map and AXI4-Stream Interfaces, is the following. Please contact Digital Blocks regarding the high-performance version.

AXI4-Stream / AXI Memory Map Address Space Conversion – Interface to DMA Controller

For larger system requiring AXI4-Stream / AXI4 Memory Map Transfers, such as a network interface with many random logic channels streaming and requiring transfers to/from host memory, the following IPs work with the DB-DMAC-MC-AXI4.

Digital Blocks DB-AXI4-STREAM-TO-AXI4-MM-BRIDGE Verilog IP Core works with Digital Blocks AXI DMA Controller to transfer data from an AXI4-Stream Interface peripheral to either memory or another peripheral.

Digital Blocks DB-AXI4-MM-TO-AXI4-STREAM-BRIDGE Verilog IP Core works with Digital Blocks AXI DMA Controller to transfer data from AXI Memory Map Address space memory or another peripheral to an AXI4-Stream Interface peripheral.

Digital Blocks Family of DMA Controller Engines

In addition to the AXI4 Memory Map to/from AXI4-Stream Interface DMA Controller IP, Digital Blocks offers a SG Memory-Map Multi-Channel Scatter-Gather DMA Controllers:

And in addition to AXI4 DMA Controllers, Digital Blocks offers AHB Multi-Channel Scatter-Gather DMA Controllers: