Reduce development costs and accelerate time to market with pre-verified IP cores

Verilog / SystemVerilog IP Cores for SoC, ASSP, ASICs and FPGAs

Digital Blocks is a leading developer of silicon-proven semiconductor Intellectual Property (IP) cores for developers requiring best-in-class IP for AMBA Peripheral such as Multi-Channel DMA / I3C / I2C / xSPI / eSPI Controllers, LCD / OLED Display Controllers & Processors, 2D Graphics Hardware Accelerator Engines, LVDS Display Link Layer Drivers, Video Signal & Image Processing, and Low-Latency UDP & RTP Hardware Protocol Stacks.

We offer synthesizable RTL Verilog & SystemVerilog IP Cores for System-on-Chip (SoC) ASSP, ASIC, and FPGA designers. At Digital Blocks we are both System Architects and ASIC/FPGA designers. Thus, we provide IP Cores with deep system-level capabilities.

Building on our IP cores, Digital Blocks design services can customize the IP core to your unique requirements.

2025 Event Schedule

Application Areas

Display Controllers – LCD & OLED Panels

Digital Blocks’ Display Controller Verilog IP Cores support a wide range of LCD/OLED display resolutions, with the standard release providing resolutions from 320×240 up to 1920×1080 Full HD. Advanced releases add capabilities for 4K and 8K display panels. The Display Controller IP drives an image to the display via on-chip AMBA interconnect connecting to Frame Buffer Memory and a Processor.

2D Graphics Hardware Accelerator Engines

Digital Blocks DB91000 BitBLT Graphics Hardware Accelerator IP renders a graphics frame by generating bitmaps from commands combining existing bitmaps on and off-screen using one of 256 Raster Operations. A Bitmap Color Expansion feature provides font expansion of compressed character bitmaps. The DB9200 2D Graphics Hardware Accelerator IP adds a Line Drawing Unit for lines, polygons, circles.

AMBA Peripherals

Digital Blocks offers best-in-class AMBA Peripherals – I2C, I3C, SPI, eSPI, SPI Execute-in-Place (XiP) for Flash memory, and Multi-Channel DMA Controllers.

Digital Blocks offers an extensive family of I2C, I3C, SPI, eSPI, and DMA Controller IPs with many system-level integration features.

We also offer Industry Standard 8255, 8259, 8279 Peripherals.

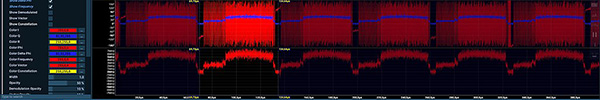

Video Signal and Image Processing

Digital Blocks Video Signal & Image Processing IP Cores perform a wide range of functions, including NTSC/PAL/SECAM Video Sync Separator, Color Space Converter, Chroma Resampler, and BT.656 Encoder & Decoder.

RTP & UDP Networking Protocol Hardware Stacks

Digital Blocks Real-Time Transport Protocol (RTP) Verilog IP Cores offer releases targeting H.264/H.265 NAL Video Streams or uncompressed RGB/YUV Video Streams. The User Datagram Protocol (UDP) Verilog IP Cores targets multimedia or data transport over a variety of Ethernet MAC speeds.

MIPI Solutions

Digital Blocks offers I3C Master/Slave, Master-only, and Slave-only IP and DSI-2 Controller (Host Version). Please contact Digital Blocks.

IP Core Featured Products

DB9000AXI Display Controller

Digital Blocks DB9000AXI4 Display Controller interfaces Frame Buffer Memory via the AMBA AXI Protocol fabric to a Display Panel with programmable resolutions from 320×240 (QVGA) up through 1920×1080 HD, 4K, and 8K.

Releases supporting baseline display requirements and advanced releases with following optional display processing features:

- Overlay Windows

- Hardware Cursor

- High Dynamic Range (HDR)

Overlay Windows option comes with advanced composition features:

- Alpha Blending

- Color Space Conversion (CSC)

- 4:2:2 YCrCb with Re-sampling & CSC to RGB

- Programmable size, placement, & format…

The DB9000 Display Controller & Processor family of IP Cores is an ASIC/FPGA design team’s most versatile choice.

AXI4 DMA Controller

The Digital Blocks DB-DMAC-MC-AXI4 Verilog RTL IP Core is a Multi-Channel DMA Controller supporting 1 – 16 independent data transfers. The DB-DMAC-MC-AXI excels at high data throughput on both small and large data sets. Standard IP releases of the number of DMA Controller Channels are 1, 2, 4, 8, 16 with development plans to expand from 32 to 256.

Releases support key features:

- Each DMA Channel has independent DMA Read and Write Controllers with top-level overhead control and parameterized FIFO

- Transfers to any combination of source or destination Memory and Peripherals

- Support for unique peripherals with sideband flow control signals

- Scatter-Gather linked-list control of data transfers with interrupt reporting

- User programmed AXI3 bursts of 1,4,8,16 beats and AXI4 bursts of 1-256 beats and full support for 4K boundary crossing

- AXI Data Width options: 8 / 16 / 32 / 64 / 128 / 256 / 512 / 1024

- Users can add verified advanced DMA features, choosing according to requirements to minimize silicon area and licensing costs

- Specification and test bench with test cases

The DMA Controller family of IP Cores contains release configurations with AXI4-Stream Interfaces for transfers between a streaming data interface and a memory-mapped interface.

eSPI Master/Slave Controller

The DB-eSPI-SPI-MS-APB Controller IP conforms to the Enhanced Serial Peripheral Interface (eSPI) Specification, satisfying the eSPI Bus Protocol and Transaction and Link Layer requirements. The DB-eSPI-SPI-MS-APB can be programmed to function as an eSPI Master or eSPI Slave, or a SPI Master or SPI Slave. Additional AMBA Interconnects supported are AXI or AHB.

SPI Master/Slave Controller

The DB-SPI-MS-AMBA is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting both Master/Slave SPI Bus transfers. The DB-SPI-MS contains an AMBA AXI, AHB, or APB Bus Interface for interfacing a microprocessor to external SPI Master/Slave devices.

SPI Master/Slave XIP Controller

The DB-SPI-XIP-FLASH-AMBA is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting access to Single/Dual/Quad/Octal SPI Flash Memory devices by way of Processor Execute-in-Place (XIP).

SPI Slave Bridge to AMBA

The DB-SPI-S-AMBA-BRIDGE is a Serial Peripheral Interface (SPI) Controller Verilog IP Core supporting transfers of SPI payload to/from a bridge APB Master (SPI2APB) Interface to user registers or memory. Releases for AXI (SPI2AXI) and AHB5 (SPI2AHB5) available.

I2C Master/Slave Controller

Digital Blocks DB-I2C-MS Controller IP Core interfaces a microprocessor via the AMBA AXI / AHB / APB Bus to an I2C Bus. Support for I2C Master and Slave functions and speeds including Standard-mode, Fast-mode, Fast-mode Plus, & Hs-mode. I2C protocol support includes features from the latest NXP I2C specification and include system-level integration features.

I2C Master Controller

Digital Blocks DB-I2C-M support I2C Master only function, at a reduced VLSI footprint. Individual releases support AMBA AXI / AHB / APB Bus

I2C Slave Controller

Digital Blocks DB-I2C-S support I2C Slave only function, at a reduced VLSI footprint. Individual releases support AMBA AXI / AHB / APB Bus

I2C Slave Bridge to AMBA

The DB-I2C-S-APB-BRIDGE processes the I2C protocol & physical layers, and receives & transmits bytes with respect to the I2C payload via a bridge APB Master (I2C2APB) Interface to user registers or memory. Releases for AXI (I2C2AXI) and AHB5 (I2C2AHB5) available.

I2C Slave with SCL Clock Only

The DB-I2C-S-SCL-CLK has SCL as the only clock, principally for configuring registers in mixed-signal ICs with low noise or low power requirements. The DB-I2C-S-SCL-CLK-APB is similar, but with a APB interface to host CPU.

Latest News

Digital Blocks DB9000 Display Controller IP Core Family Extends Leadership in 8K, Automotive, Medical, Aerospace, and Industrial SoC Designs

GLEN ROCK, New Jersey – December 28, 2025 – Digital Blocks, a leading developer of silicon-proven semiconductor Intellectual Property (IP) soft cores, …

Digital Blocks AMBA Multi-Channel DMA Controller IP Core Family Extends Leadership with releases for core DMA Engines in RISC-V® & ARM® Systems and Peripherals to Memory Applications.

GLEN ROCK, New Jersey, January 14, 2024 – Digital Blocks, a leading developer of silicon-proven semiconductor Intellectually Property (IP) soft cores …

Digital Blocks AMBA Peripherals I3C, I2C, eSPI, xSPI Controller IP Core Families Extend Leadership with enhancements containing feature-rich, system-level integration features.

GLEN ROCK, New Jersey, January 8, 2023 – Digital Blocks, a leading developer of silicon-proven semiconductor Intellectually Property (IP) soft cores …